AVSBus v2.0 Verification IP

Truechip's AVSBus Verification IP provides an effective and efficient way to verify the components interfacing with AVSBus interface of an IP and SOC. Truechip's AVSBus VIP is fully compliant to AVSBus Specification version 2.0. The VIP is lightweight with easy plug-and-play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest level of quality.

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment.

Features

- Fully compliant with AVSBus Specification as defined in version v2.0 & seamlessly integrated with PMBus Specification v1.4.

- Supports topologies with one controller–one target as well as multi-link configurations.

- Supports 3-wire bidirectional AVSBus communication mode.

- Supports 4-bit Target Address field for multi-target configuration up to 15 targets.

- Supports AVSBus data format, including numeric values represented using standard two's complement.

- Supports necessary conversions between AVSBus and PMBus data formats.

- Supports detection and handling of communication timeouts.

- Supports generation of alerts by the master on status change indication.

- Supports frame alignment and allows execution of continuous back-to-back command frames.

- Supports user-defined response frame handling for status monitoring.

- Enables clock suspension during idle periods.

- Supports a mechanism for controller to abort frame and to orderly initiate a new frame.

- Supports 96 bit structured support for both read and write frame transactions.

- Supports 2-8 bit Startcode along with marker bits.

- Supports all read and write types, including “Write-and-Commit”, “Write-and-Hold” and “Commit” operations.

- Supports generation of transactions with UVM register model.

- Built in Bus Monitor provides extensive protocol checking.

- Supports Dynamic as well as Static Error Injection & detection scenarios.

- Invalid StartCode pattern injection

- 3-bit CRC error injection

- Invalid selector testing

- Unsupported command type errors

- Command group violations

- Invalid command data types

- Unavailable resource simulation

- Reserved bit field violation checks

- Signal validity checks during clock suspension

- On the fly protocol checking using protocol check functions, static and dynamic assertion.

- Built in Coverage analysis.

- Provides a comprehensive user API (callbacks) in Transmitter & Receiver.

- Graphical analyser for all Layers to show transactions for easy debugging.

Deliverables

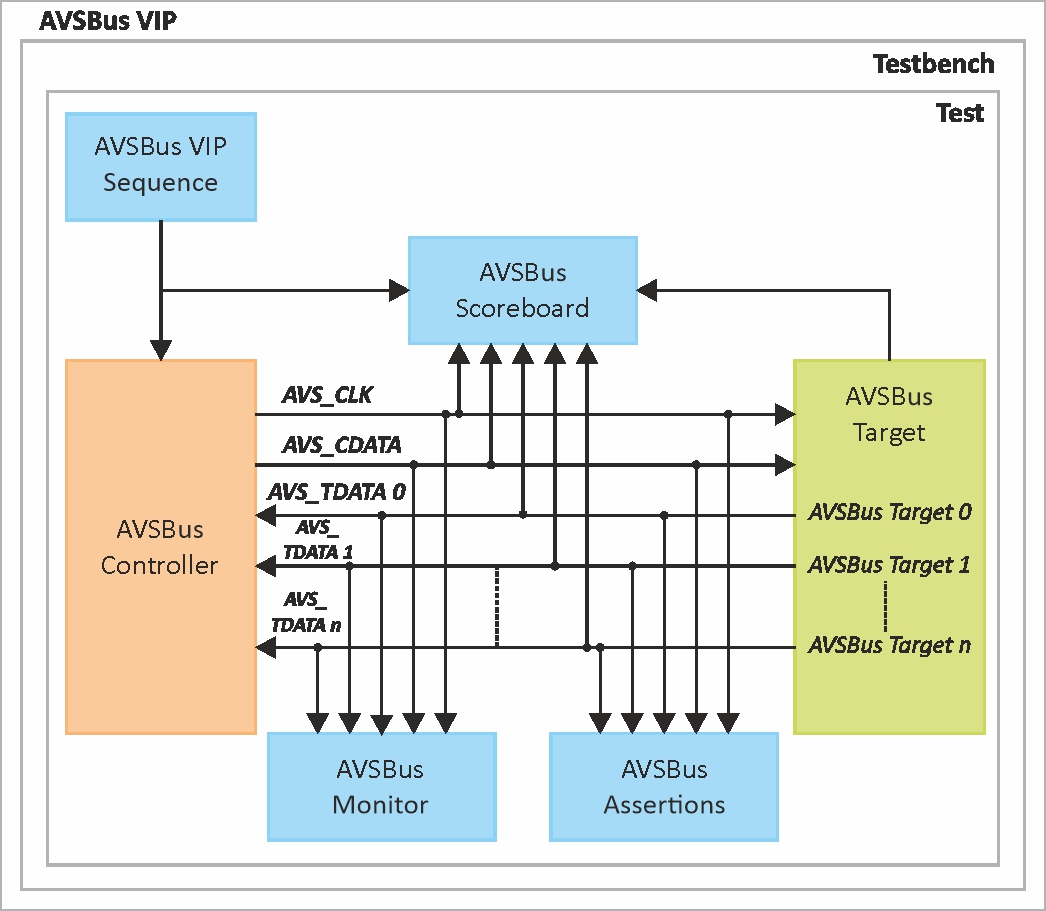

- AVSBus Controller/Target BFM/Agent.

- AVSBus Monitor and Scoreboard.

- Testbench Configurations.

- Test Suite (Available in Source Code).

- Basic and Directed Protocol Tests.

- Random Tests.

- Error Scenario Tests.

- Assertions & Coverage Tests.

- Integration Guide, User Manual and Release Notes